Game Plan

Let's try to picture what needs to happen.

- Assume PC has just been updated, but the instruction has yet to

be fetched. Recall the PC holds the address of the current instruction

being executed, yet it also has to be updated to the address of the next

instruction to be executed. So at this point, we getting ready to fetch

that next instruction.

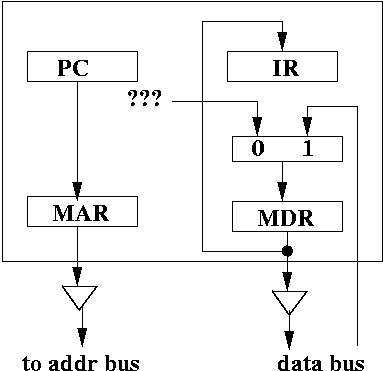

- Recall that we need to get the address to memory and the only

way to do that is to get the address from PC to the address bus.

The problem? The PC is not directly hooked to the address bus.

Only the MAR is hooked to the address bus. So we need to get

the PC to the MAR. Thus, we need to perform the following

RTL statement.

MAR <- PC

- At this point, we need to go to a new state. The reason

is that in each state, we perform the load last, and we need the

value in MAR before we put the address of the MAR onto the

address bus.

- In the new state, we need to set signals to memory.

In particular, we need to active the tri-state buffers from the

MAR to the address bus. We need to send CE = 1 and

R/\W = 1 to indicate we want to do a read from memory.

We're going to assume that memory is slow. Thus, we will remain in this state until we receive an ACK = 1. This is a signal from memory to the CPU indicating it has placed the data (which is the instruction) onto the data bus.

When we get ACK = 1, we transition to a new state. In this state, we must still have CE = 1, R/\W = 1MARout (which enables the tri-state buffers).

Why do these signals have to occur? Once the ACK = 1 is sent from memory to the CPU, why do we need to keep asserting the signals to memory?

The reason is that the MDRload occurs near the end of the clock cycle, and we want the signals to memory to be maintained until that time. By setting CE = 0, we're telling memory we're done and it no longer has to place the value on the data bus. However, we aren't done until MDR has loaded the instruction. Recall the MDR is hooked up to the data bus, and is the only connection from the CPU to the data bus.

Once we've performed the load, we transition to a new state, where we can set CE = 0, which finally indicates we're done with memory. Furthermore, we can load IR with the data from the MDR.

For convenience, let's assume that if signal CE is in the state, then CE = 1, and if it's not in the state, then CE = 0.

Finite States

| State 1 |

MAR <- PC ----------------- MARload goto State 2 |