Introduction

- Fetch instruction

- Decode instruction/Fetch Operands The operands can come from the register file, or from the instruction (e.g., immediate values and offset) or both.

- Perform ALU operations Mostly this involves introducing MUXes so that we can select which data to send to the X and Y input of the ALU.

- Access memory for load/store operations

We're now at the fifth step which is Store result of ALU operations. We could have done this at step 4, but we can think of storing the result as also an opportunity to store the result of any load operations, which was done in step 4.

This step is straight-forward. At this point, the ALU should be generating the result. Recall that this result was performed in step 3 and we're needing to store it in step 5. If the ALU had to be used for something else between step 3 and 5, we could put a register at the output of the ALU and store the result in a temporary register, placing the result back to the register file at some later point.

It turns out that you want to do this if you plan to convert this CPU to a pipelined CPU. Since that's an advanced topic, we won't do that right now.

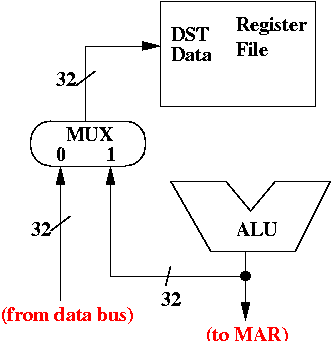

Recall from the previous set of notes that we sent the data bus to DST Data (for load operations). However, we're also going to have to send the output of the ALU to DST Data. Clearly, we can't have both signals going there at the same time. We need a way to choose between the two sets of signals.

We need a MUX. In particular, a 32-bit 2-1 MUX.

Diagram Showing How Results are Stored

This is clearly NOT a complete diagram, but should contain enough information to figure out what's going on.

The result of the ALU is fed to one of two places. It is sent to the MAR, for use in load/store functions. (The MAR has a MUX as well to pick from the ALU or from the PC).

It also goes to a MUX. The MUX is drawn with the inputs on the bottom and the output on the top. However, it's still a MUX. It still selects from more than one input.

The MUX has two 32-bit inputs. One input comes from the data bus, and is used in load operations. The other input comes from the ALU, which is for the stored result. The second is more commonly used since ALU operations should occur more frequently than memory operations.