The assumption about I/O devices is that it's really, really slow, compared to the speed of the CPU. I/O devices include keyboard, mouse, printers, etc. While some devices may need quick response, usually when downloading or uploading data, I/O devices are generall considered slow.

Rather than the CPU "polling" or asking the I/O device if it needs some action taken on its behalf, the I/O device interrupts the CPU by sending an interrupt signal (such as a positive edge). The CPU then temporarily stops what it is doing, and services the I/O device.

The code to do this is called the interrupt handler. The handler must already be loaded in memory before the interrupt has occurred (often it's already there when the machine boots up).

Occasionally, an I/O device needs to read from memory or write to memory. This can be very slow, as we shall see.

Now imagine that the I/O device wants to store a lot of data to memory. Perhaps you have just taken some pictures on a digital video camera, and want to store this information.

One way to do this is to alert the CPU that the I/O device wants to store data to memory. These are the steps that might be taken.

Thus the data flows from the I/O device to the CPU, and from the CPU to memory.

After all, how can memory who is sending signals to it? How does it know that the CPU sends signals, instead of the device itself.

If the I/O device generates all the signals that the CPU does, then the I/O device can bypass the step where the data transfers to the CPU, thus, potentially doubling the speed.

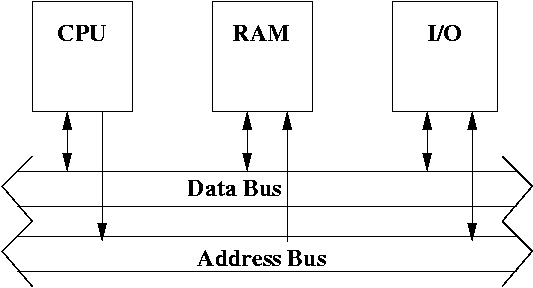

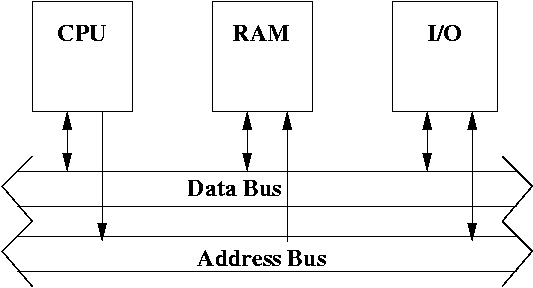

With I/O devices, both the CPU and the I/O device may be contending to use the address and data bus, so there needs to be some way of arbitrarting (deciding) who gets the bus at which time.

Furthermore, if there are more than one I/O devices trying to access the bus, we may have to decide which I/O device gets control.

One potential solution to the problem is to have a hardware device that is a bus arbitrator, which decides which device gets the bus, and helps coordinate who sends what signals to the memory.